<section-header><list-item><list-item><list-item><list-item><list-item><list-item>

Outline

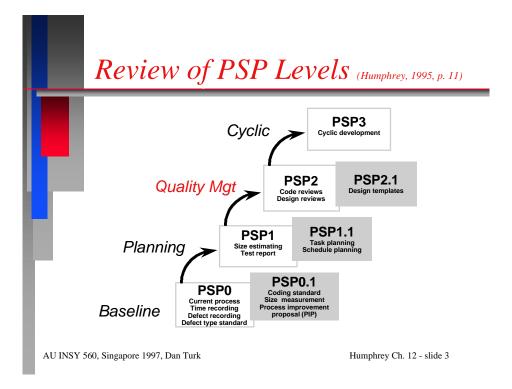

• Review of PSP Levels

• Overview

• Overview

• Selecting Verification Methods

• Design Standards

• Sate Machines

• Program Tracing

• Design Correctness

## Selecting Verification Methods

(cf. Humphrey, 1995, p. 374-376)

| Verification Methods    |                |                                       |

|-------------------------|----------------|---------------------------------------|

| Humphrey (1995, p. 375) |                |                                       |

| M ethod                 | Application    | C o m m e n t s                       |

| Loop                    | Program        | Use on loop logic whenever            |

| V erificatio n          | Loops          | practical.                            |

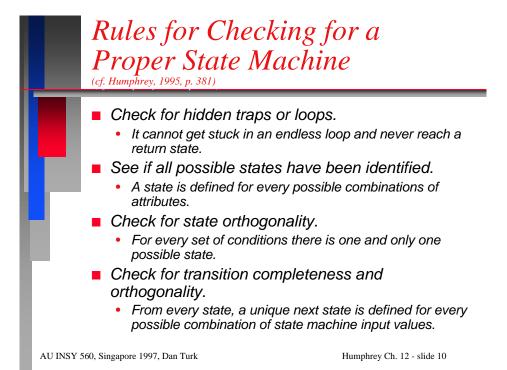

| Proper State            | State          | Use during design and in reviews and  |

| M achines               | M achines      | inspections on every state m achine.  |

|                         | Only           |                                       |

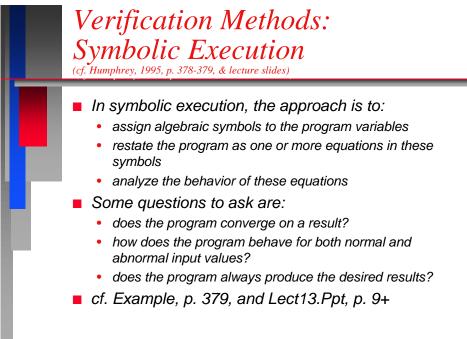

| Sym bolic               | A lg orithm ic | Use whenever it applies.              |

| Execution               | Logic          |                                       |

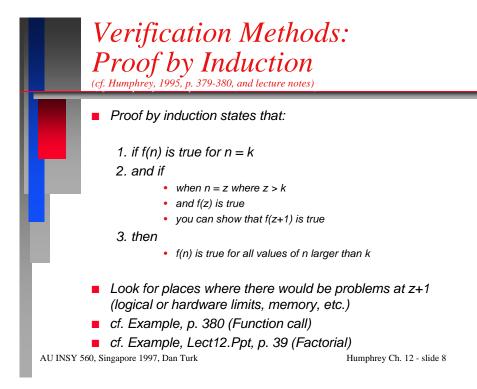

| Proof by                | Loops &        | Use in conjunction with trace tables. |

| Induction               | Recursion      |                                       |

| Trace Tables            | Complex        | Use for small program elements and    |

|                         | Logic          | with proof by induction and/or        |

|                         | 0              | sym bolic execution w henever         |

|                         |                | possible. U se if other verification  |

|                         |                | methods do not apply.                 |

| Execution               | Complex        | Use for small program elements and,   |

| Tables                  | Logic          | as a last resort, when no other       |

|                         | -              | methods apply.                        |

| Form al                 | Entire         | Use whenever you know how to          |

| V erification           | Program        | apply the verification methods, they  |

|                         | -              | appear feasible, and they are cost    |

|                         | 1              | effective.                            |

Select appropriate methods based on:

- Your defect profile: Use verification where you have problems.

- Effectiveness of your current methods: Use methods you know and are effective with.

• Economics of your methods: Use the most cost-effective methods. AU INSY 560, Singapore 1997, Dan Turk Humphrey Ch. 12 - slide 5

AU INSY 560, Singapore 1997, Dan Turk

- A program is likely a state machine if, with identical inputs, it behaves differently at different times.

- Example: LOC counter

- comments

- non-comments (program, executable)

- In a proper state machine:

- *it is possible to reach a program return state from every other state*

- all state conditions are complete and orthogonal

- all transitions from each state are complete and orthogonal

AU INSY 560, Singapore 1997, Dan Turk

AU INSY 560, Singapore 1997, Dan Turk

Humphrey Ch. 12 - slide 17

## Comments on Verification Methods (cf. Humphrey, 1995, p. 436-437) If you have any question about the validity of the design, perform verification. Test at least a single case, even when confident

- Test at least a single case, even when confident of the design.

- Design down, verify up.

- Verify all cases.

- Track time spent in verification and assess costeffectiveness of approaches after you become familiar with the techniques.

- "When you verify your designs as you produce them, your design verification data can greatly accelerate your design reviews."

AU INSY 560, Singapore 1997, Dan Turk